## UNIVERSITE Mohamed Boudiaf DE M'SILA FACULTE DE TECHNOLOGIE 2ème ANNEE LICENCE (ELN,ELT)

### **Travaux Pratiques**

# Logique Combinatoire et Séquentielle

TP N°3

#### ADDITIONNEUR ET SOUSTRACTEUR À 4 BITS

|        |    | Nom et prénom | Groupe |

|--------|----|---------------|--------|

|        | 01 |               |        |

| $\sim$ | 02 |               |        |

|        | 03 |               |        |

| Ф                                     | Evaluation            | Pts   | Pourcentage<br>de réalisation | Note | Signature de<br>l'enseignant |

|---------------------------------------|-----------------------|-------|-------------------------------|------|------------------------------|

| ◊   ⊽                                 | Partie théorique      | 6 pts | %                             | /6   |                              |

| العار// اا                            | Expérience 01         | 2 pts | %                             | /2   |                              |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Expérience 02         | 3 pts | %                             | /3   |                              |

|                                       | Expérience 03         | 4 pts | %                             | /4   |                              |

|                                       | Niveau de<br>maîtrise | 5 pts | %                             | /5   |                              |

|                                       |                       |       | Note globa                    | ıle  | /20                          |

|    | Nom et prénom |

|----|---------------|

| 01 |               |

| 02 |               |

| Fait le | / | /2020 |

|---------|---|-------|

| Fait le |   | /2    |

#### But du TP & matériel

Le but de ce TP est de faire l'analyse et la réalisation d'un circuit arithmétique à base de portes logiques en prenant l'additionneur comme exemple, l'étudiant va : 1) Comprendre et différencier entre un demi-additionneur et un additionneur complet.

2) Déduire leurs tables de vérité, écrire leurs fonctions logiques à partir de ces derniers, Les simplifier et les réaliser puis faire la comparaison avec un additionneur à circuit intégré.

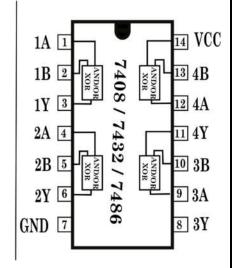

Alimentation 5V, plaque d'essai, fils de connexion, LEDs, résistances et circuits intégrés (7408,7432, 7486 et 7483).

#### Ce que vous devrez savoir

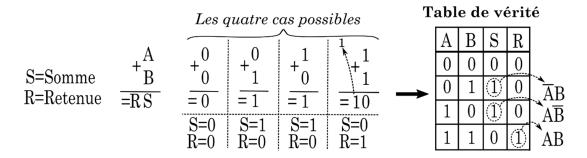

Les opérations arithmétiques (+, -, x, /) en électronique numérique (calculatrice, microporcesseur) se font en système binaire, Il s'agit d'une opréation entre deux nombre binaires, ('0' et/ou '1'). Si on prend l'exemple de l'opération d'addation, on constate qu'il y a quatre cas possibles, qu'on peut les écrire dans une table de verité de la manière suivante :

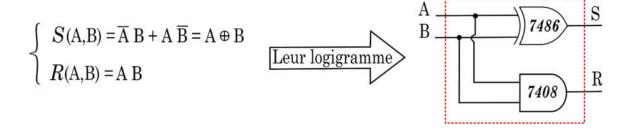

Les deux sorties (S et R) de la table de verité sont considérées des fonctions logiques, elles sont écrites en fonction de deux variables d'entrée (A et B) sous la forme suivante :

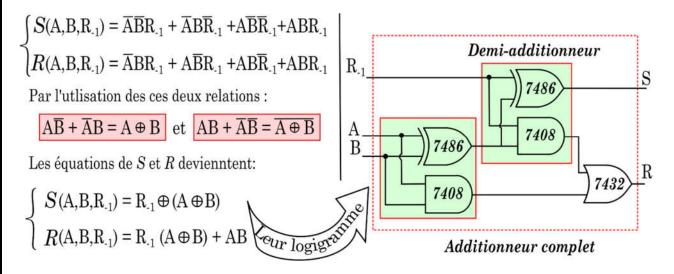

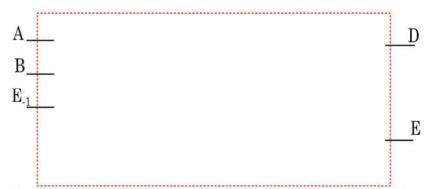

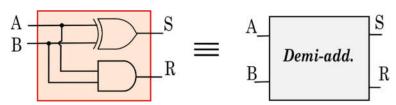

Le circuit à l'interieur du rectangle pointu s'appel **un demi-addtionneur,** il fait l'addition de deux nombres binaires sans tenir en compte de la retenue précedente. De ce fait :

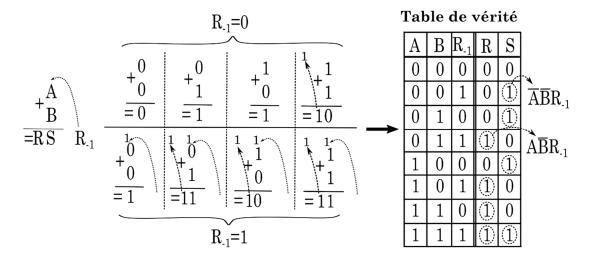

Un addtionneur complet fait l'addtion de trois nombres, les deux nobmres binaires (A et B) plus la retenue de l'étage précédent R<sub>-1</sub> si elle existe.

A partir de la table de vérité, les fonctions logiques S et R prennent les sormules suivante :

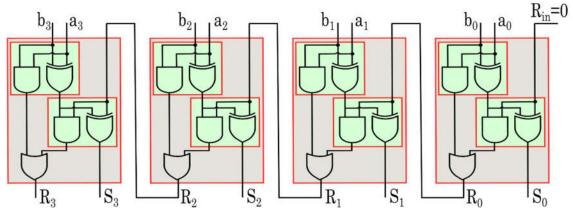

Additionneur à 4 bits: En realité, les nombres binaires sont composés de plus d'un bit, à cet effet, pour faire la somme de deux nombres (A=a3a2a1a0 et B=b3b2b1b0) de 4 bits chacun, il nous faut 4 blocs d'additionneur complet, qui seront cablés de la manière suivante :

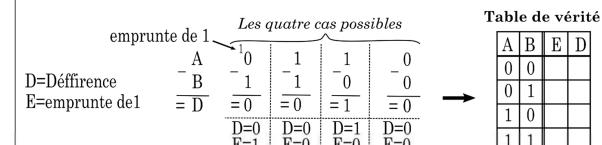

Si vous savez que l'opération de soustraction en système binaire est également basée sur les quatre cas de sousraction à deux bits présentés ci-après:

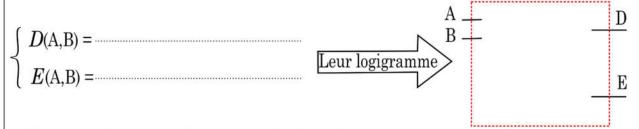

- Compléter la table de vérité de demi-soustracteur et déduire les équations logiques de deux variables de sortie (D et E ) puis tracer leur logigramme.

- Si on prend en compte la retenue précedente, le demi-soustracteur devient un soutracteur complet et sa table vérité s'écrit comme suit:

| A | В | $\mathbf{E}_{\text{-}1}$ | Ε | D |

|---|---|--------------------------|---|---|

| 0 | 0 | 0                        | 0 | 0 |

| 0 | 0 | 1                        | 1 | 1 |

| 0 | 1 | 0                        | 1 | 1 |

| 0 | 1 | 1                        | 1 | 0 |

| 1 | 0 | 0                        | 0 | 1 |

| 1 | 0 | 1                        | 0 | 0 |

| 1 | 1 | 0                        | 0 | 0 |

| 1 | 1 | 1                        | 1 | 1 |

$$\begin{cases} D = \\ E = \end{cases}$$

$E \mid D$

Donner les fonctions logiques des variables de sortie D et E et tracer leur logigramme

#### Ce que vous devrez réaliser

**Réaliser** à l'aide des portes logiques le circuit d'un demi-additionneur et d'un additionneur complet et **remplir** leurs tableaux de mesure suivantes :

Tableau de mesure d'un demi-additionneur

| A  | В  | R | S |

|----|----|---|---|

| 0V | 0V |   |   |

| 0V | 5V |   |   |

| 5V | 0V |   |   |

| 5V | 5V |   |   |

Tableau de mesure d'un additionneur complet

| A  | В  | R.1 | R | S |

|----|----|-----|---|---|

| 0V | 0V | 0V  |   |   |

| 0V | 0V | 5V  |   |   |

| 0V | 5V | 0V  |   |   |

| 0V | 5V | 5V  |   |   |

| 5V | 0V | 0V  |   |   |

| 5V | 0V | 5V  |   |   |

| 5V | 5V | 0V  |   |   |

| 5V | 5V | 5V  |   |   |

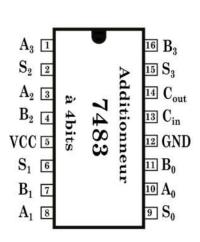

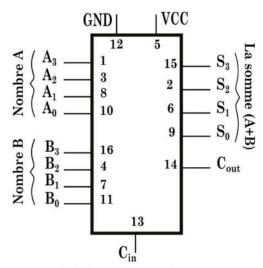

Additionneur à circuit intégré : Le schéma de l'additionneur de deux nombres à 4 bits décrire dans la section précédente représente le schéma interne de l'additionneur à 4 bits à circuit intégré 7483, dont son brochage et son câblage est le suivant :

Schéma de brochage

Schéma de câblage

- Utiliser ce circuit (7483) pour réaliser un montage qui vous permettra de calculer la somme de deux nombres A et B (à 4 bits) donnés dans le tableau suivant :

| A <sub>3</sub> | $A_2$ | A <sub>1</sub> | A <sub>0</sub> | $\mathbf{B}_3$ | $B_2$ | B <sub>1</sub> | B <sub>0</sub> | Cout | $S_3$ | $S_2$ | $S_1$ | S <sub>0</sub> |

|----------------|-------|----------------|----------------|----------------|-------|----------------|----------------|------|-------|-------|-------|----------------|

| 0              | 0     | 1              | 0              | 0              | 0     | 1              | 1              |      |       |       |       |                |

| 0              | 1     | 0              | 0              | 0              | 1     | 1              | 0              |      |       |       |       |                |

| 1              | 0     | 0              | 0              | 1              | 0     | 0              | 1              |      |       |       |       |                |

| 1              | 1     | 0              | 1              | 1              | 0     | 1              | 1              |      |       |       |       |                |

#### Niveau de maîtrise

En utilisant le schéma bloc d'un demi-additionneur (donné ci-dessous), **Tracer** le logigramme d'un additionneur de deux nombres à trois bits chacun ( $A=A_2A_1A_0$  et  $B=B_2B_1B_0$ ).

| A <sub>0</sub> —                 |                  |

|----------------------------------|------------------|

| B <sub>0</sub> —                 |                  |

|                                  | — S <sub>0</sub> |

|                                  |                  |

| A <sub>1</sub>                   | $$ $S_1$         |

| B <sub>1</sub>                   |                  |

|                                  |                  |

|                                  | S <sub>2</sub>   |

| $A_2$                            |                  |

| A <sub>2</sub><br>B <sub>2</sub> |                  |

|                                  |                  |

|                                  |                  |

|                                  |                  |

|                                  |                  |