#### Mémoires

# I.1. Définitions

Une mémoire est un composant électronique dans lequel on peut enregistrer et resituer des informations sous forme binaire. Ces informations peuvent être écrites ou lues.

Il y a:

Ecriture : Lorsqu'on enregistre des informations en mémoire.

Lecture : lorsqu'on récupère des informations précédemment enregistrées dans la mémoire.

Une mémoire peut être représentée comme une table constituée d'un ensemble de lignes.

Chaque ligne représente alors une case mémoire qui ne peut contenir qu'une seule donnée.

| Adresse | Case mémoire |

|---------|--------------|

| 111     |              |

| 110     |              |

| 101     |              |

| 100     |              |

| 011     |              |

| 010     |              |

| 001     |              |

| 000     | 10010100     |

Chaque ligne est identifiée par un numéro appelé adresse. Chaque donnée devient alors accessible grâce à son adresse.

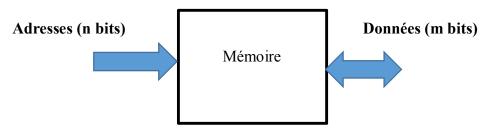

Le nombre de fils d'adresses d'un boîtier mémoire définit le nombre de cases mémoire que comprend le boîtier **Figure (I.1)**. Avec une adresse de **n bits** il est possible d'adresser au plus **2**<sup>n</sup> cases mémoires. Le nombre de fils de données définit la taille des données que l'on peut extraire ou sauvegarder dans chaque case mémoire (toujours une puissance de 2).

Fig I.1. Mémoire

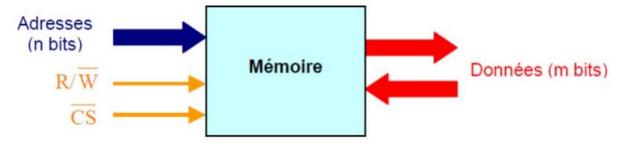

En plus du bus d'adresses et du bus de données, un boîtier mémoire comprend Figure (I.2) :

- Une entrée de commande  $(R/\overline{W})$  qui permet de définir le type d'opération que l'on effectue avec la mémoire (lecture/écriture)

- Une entrée de sélection (*CS*) qui permet de mettre les entrées/sorties du boîtier en haute impédance.

Fig.I.2. Constitution d'une mémoire

Une opération de lecture ou d'écriture de la mémoire suit toujours le même cycle :

- 1. Spécifier l'adresse

- 2. Choisir de l'opération à effectuer  $(\mathbf{R} / \overline{\mathbf{W}})$

- 3. Sélectionner la mémoire ( $C\overline{S}$ )

- 4. Effectuer l'opération (lecture ou écriture)

**Capacité** : C'est le nombre total de bits que contient la mémoire. Elle s'exprime aussi souvent en octet.

**Format des données** : C'est le nombre de bits que l'on peut mémoriser par case mémoire. On dit aussi que c'est la largeur du mot mémorisable.

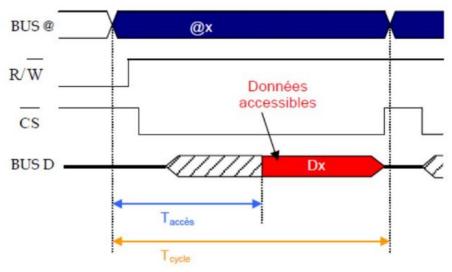

**Temps d'accès** : c'est le temps qui s'écoule entre l'instant où a été lancée une opération de lecture/écriture en mémoire et l'instant où la première information est disponible sur le bus de données.

**Temps de cycle** : il représente l'intervalle minimum qui doit séparer deux demandes successives de lecture ou d'écriture. Il est toujours supérieur au temps d'accès car on a besoin d'opérations supplémentaires entre 2 accès (stabilisation des signaux, synchronisation ...)

Exemple : Chronogramme d'un cycle de lecture **Figure (I.3)**.

Fig.I.3. Chronogramme d'un cycle de lecture

#### I.2. Mode d'accès à l'information

### 1. Accès séquentiel

Pour accéder à une information on doit parcourir toutes les informations précédentes (accès lent)

Exemple : bandes magnétiques (K7 vidéo)

**2. Accès direct** : Chaque information a une adresse propre. On peut accéder directement à chaque adresse

Exemple : mémoire central

3. Accès semi-séquentiel : intermédiaire entre séquentiel et direct

Exemple : disque dur (accès direct au cylindre, ensuite accès séquentiel au secteur sur un cylindre)

**4. Accès associatif** : une information est identifiée par une clé. On accède à une information via sa clé

Exemple: mémoire cache

## I.3. Types de mémoires

Les mémoires sont maintenant des composants électroniques à base de transistors.

## I.3.1. Mémoires vives : RAM (Random Access Memory)

- 1. Mémoire accessible en lecture et écriture

- 2. Mémoire volatile interne.

Il existe deux types de mémoires RAM qui se distinguent par leur technique de fabrication Mémoires statiques appelées **SRAM** pour Static RAM.

Mémoires dynamiques appelées **DRAM** pour Dynamic RAM.

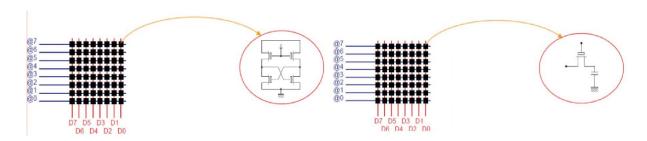

Le bit mémoire d'une **SRAM** est composé d'une bascule (généralement bascule D). Chaque bascule contient entre 4 et 6 transistors. Par contre dans les **DRAM**s, l'information est mémorisée sous la forme d'une charge électrique stockée dans un condensateur, en plus d'un transistor de commande **Figure (I.4) a, b** respectivement.

Fig.I.4. a) Constituants d'un SRAM b) un DRAM

## **Avantages**

Cette technique permet une plus grande densité d'intégration, car un point mémoire nécessite environ quatre fois moins de transistors que dans une mémoire statique. Sa consommation s'en retrouve donc aussi très réduite.

#### Inconvénients

## 1. Rafraîchissement

Ce rafraîchissement indispensable a plusieurs conséquences :

Il complique la gestion des mémoires dynamiques car il faut tenir compte des actions de rafraîchissement qui sont prioritaires.

la durée de ces actions augmente le temps d'accès aux informations.

#### 2. Réécriture

La lecture de l'information est destructive. En effet, elle se fait par décharge de la capacité du point mémoire lorsque celle-ci est chargée. Donc toute lecture doit être suivie d'une réécriture.

### **SRAM VS DRAM**

| Mémoire dynamique            | Mémoire statique             |

|------------------------------|------------------------------|

| Grande densité d'intégration | Petite densité d'intégration |

| Bon marché                   | Chère                        |

| Lente                        | Rapide                       |

| Mécanisme de rafraîchissent  |                              |

Comme son coût est moindre et que sa densité d'intégration est supérieure, la mémoire dynamique est utilisée pour la mémoire principale de l'ordinateur. Par contre, la mémoire statique est utilisée pour les caches en raison de sa plus grande vitesse.

Il existe deux types principaux de mémoire dynamique qui se distinguent par leur façon de communiquer avec le processeur :

- ✓ Les mémoires dynamiques asynchrone

- ✓ Les mémoires dynamiques synchrones, appelées SDRAM pour Synchronous Dynamic RAM.

## **DRAM ASYNCHRONE**

Lorsque le processeur lit une donnée dans une mémoire asynchrone, celui-ci lui envoie l'adresse puis attend que celle-ci lui retourne la donnée à cette adresse.

- Plusieurs cycles horloge peuvent s'écouler avant que la donnée ne parvienne au processeur.

- Après réception de la donnée, le processeur peut à nouveau demander une autre donnée à la mémoire.

- À chaque requête à la mémoire, le processeur reste inactif en attendant que la donnée n'arrive.

#### **SDRAM**

Dans le cas de mémoire synchrone, le processeur peut envoyer à la mémoire une nouvelle requête de lecture ou d'écriture avant que celle-ci n'ait fini de traiter la première requête.

- Les demandes successives sont alors exécutées séquentiellement par la mémoire.

- Chaque requête est reçue pendant un cycle d'horloge et les données sont délivrées quelques cycles d'horloge plus tard.

- Le nombre de cycles d'horloge entre la requête et la donnée est fixe. Ainsi, le processeur peut déterminer à quelle requête correspond chaque donnée.

# Principe de fonctionnement d'une mémoire synchrone

Il est identique au pipeline utilisé pour réaliser un processeur :

- ✓ La mémoire est organisée comme une chaîne où sont traitées les requêtes.

- ✓ La mémoire traite simultanément plusieurs requêtes qui se trouvent à des étapes différentes de la chaîne.

- ✓ Le traitement d'une seule requête prend plusieurs cycles d'horloge mais une requête est traitée à chaque cycle.

Parmi les mémoires synchrones, on distingue encore plusieurs variantes :

- ✓ **SDR SDRAM** pour Single Data Rate **SDRAM** qui reçoivent une requête à chaque cycle d'horloge.

- ✓ DDR SDRAM pour Double Data Rate DRAM qui permettent de doubler le débit de données entre le processeur et la mémoire. Une requête est encore traitée à chaque cycle d'horloge mais chaque requête concerne deux mots consécutifs en mémoire. Le premier mot est transmis sur le front montant du signal d'horloge alors que le second est transmis sur front descendant du signal d'horloge.

- ✓ **DDR2 SDRAM** doublent encore le débit de données en traitant quatre mots consécutifs en mémoire à chaque requête.

# Mémoires mortes ROM (Read Only Memory)

- 1-Mémoire accessible en lecture (l'écriture est programmable)

- 2-Mémoire non volatile interne.

Pour certaines applications, il est nécessaire de pouvoir conserver des informations de façon permanente même lorsque l'alimentation électrique est interrompue. On utilise alors des mémoires non volailles appelées mémoires mortes ou mémoires à lecture seule (ROM : Read Only Memory). Ces mémoires, contrairement aux RAM, ne peuvent être que lue. L'inscription (ou écriture) en mémoire des données restent possible mais est appelée programmation.

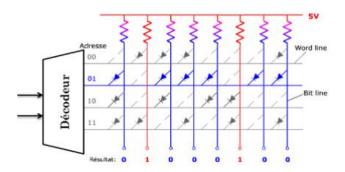

**ROM** (classique) est programmée par le fabricant et son contenu ne peut plus être ni modifié, ni effacé par l'utilisateur. Cette mémoire est composée d'une matrice dont la programmation s'effectue en reliant les lignes aux colonnes par des diodes. L'adresse permet de sélectionner une ligne de la matrice et les données sont alors reçues sur les colonnes (le nombre de colonnes fixant la taille des mots mémoire) **Figure (I.5)**.

Fig.I.5. Mémoire ROM

Suivant la méthode de programmation, plusieurs types de ROM existent :

PROM (Programmable ROM) est une ROM qui peut être programmée une seule fois par l'utilisateur. Les liaisons à diodes de la ROM sont remplacées par des fusibles pouvant être détruits ou des joncions pouvant être court-circuitées Figure (I.6).

Fig.I.6. PROM

■ **EPROM** (Erasable Programmable ROM) ou UV-EPROM est une PROM qui peut être effacée par Ultraviolet (UV) **Figure (I.7)**.

Fig.I.7. UV EPROM

- **EEPROM** (Electrically EPROM) est une mémoire programmable et effaçable être effacée par un simple courant électrique. Elle utilise 2 à 3 transistors pour mémoriser un bit.

- **FLASH EPROM** est une EEPROM qui utilise qu'un seul transistor pour mémoriser un bit.

Actuellement, les mémoires EEPROM et Flash sont le plus souvent utilisées. Les EEPROM, servent à mémoriser des données de configuration, qu'on modifie rarement, tel que :

- ✓ **Chargeur d'amorce** : qui est un programme permettant de charger le système d'exploitation en mémoire vive et de le lancer.

- ✓ **POST (Power-On Self Test)** est un programme exécuté automatiquement à l'amorçage du système permettant de faire un test du système.

- ✓ **Setup CMOS** : est l'écran disponible à l'allumage de l'ordinateur permettant de modifier les paramètres du système ;

- ✓ **BIOS** : est un programme permettant de piloter les interfaces d'entrée/sortie d'un ordinateur.

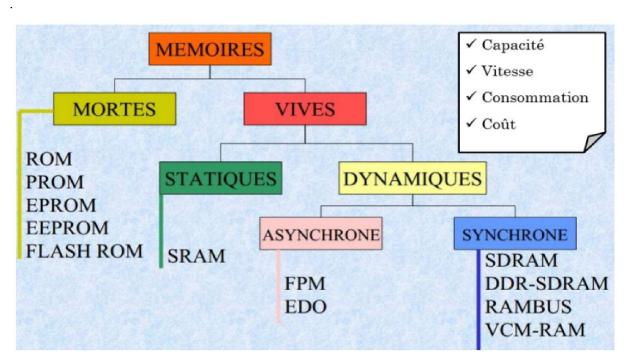

#### Critères de choix d'une mémoire

Les critères de choix d'une mémoire sont donnés par la Figure (I.8).

Fig.I.8. Critères de choix d'une mémoire

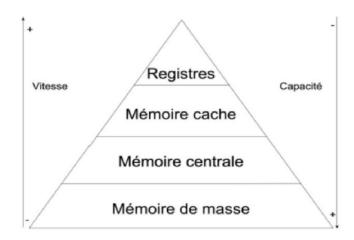

#### Hiérarchie mémoire

L'ordinateur contient différents niveaux de mémoire, organisés selon une hiérarchie mémoire **Figure (I.9)**.

Fig.I.9. Hiérarchie mémoire

# Associations de blocs mémoires

En pratique les circuits mémoires ont des caractéristiques ne leur permettant pas de satisfaire directement les exigences d'espace mémoires dans les systèmes électroniques. On associe donc différents circuits mémoire sain de remplir ces exigences à savoir augmenter la zone adressable

et ou la largeur des mots mémoires. On procède pour cela soit à un agrandissement du bus de données (association parallèle), soit à un agrandissement du bus d'adresse (association série), soit les deux à la fois.

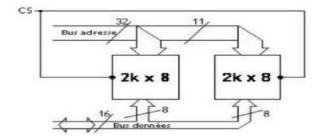

Association en parallèle : On effectue une mise en parallèle des blocs mémoires élémentaire afin d'augmenter la largeur des mots, c'est-à-dire la largeur du bus de données, le bus d'adresse commun aux blocs élémentaire restant inchangé. On pourrait par exemple associer en parallèle 4 blocs mémoires de 8 bits pour former un mots mémoires de 32 bits Figure (I.10).

Fig.I.10. Association en parallèle

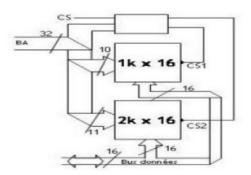

Association en série : On effectue une association série des blocs mémoires pour augmenter le nombre de mots mémoires, c'est-à-dire la capacité de la zone adressable. Pour ce faire on augmente la largeur du bus d'adresse **Figure (I.11)**.

Fig.I.11. Association en série