Electronique Numérique Avancée FPGA +VHDL

Topic outline

-

-

Forum

-

-

Le chapitre 1 traite les différents réseaux logiques programmables tels que les PLA, PAl, GAL, CPLD et FPGA en présentant leurs structures et leur classifications

Le chapitre 1 traite les différents réseaux logiques programmables tels que les PLA, PAl, GAL, CPLD et FPGA en présentant leurs structures et leur classifications-

File

TD 1 relatif au chapitre1 du cours ENA

-

-

Ce chapitre traite les technologies de fabrication des circuits logiques programmables (EPROM, EEPROM, PAL, PLA, CPLD et FPGA). Il détaille les circuits programmables à fusible, à anti-fusiles, les MOS à grille flottante les RAM statiques qui constituent les briques de base de ces derniers.

Ce chapitre traite les technologies de fabrication des circuits logiques programmables (EPROM, EEPROM, PAL, PLA, CPLD et FPGA). Il détaille les circuits programmables à fusible, à anti-fusiles, les MOS à grille flottante les RAM statiques qui constituent les briques de base de ces derniers.

-

-

-

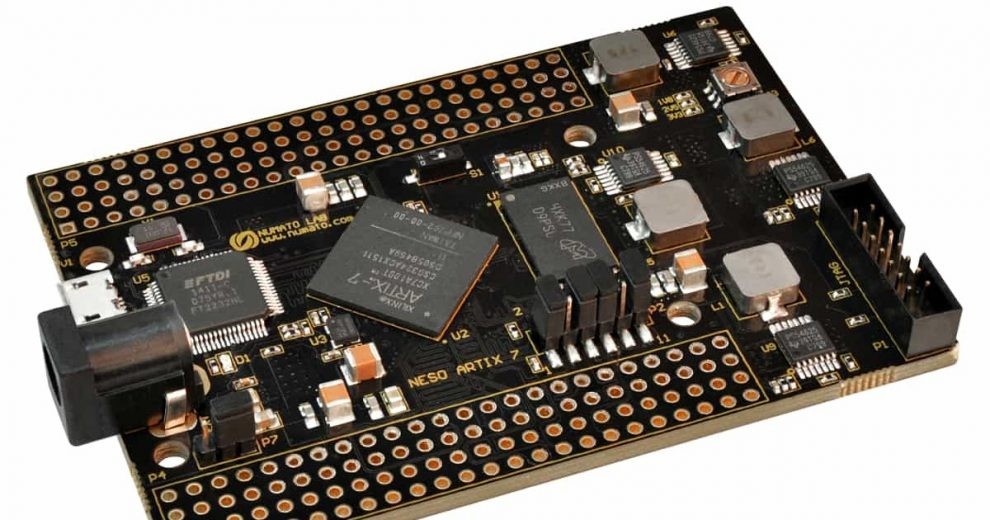

Ce chapitre détaille les différentes architectures des circuits FPGA tels que :

- Tableau symétrique.

- En colonne.

- Mers de portes.

- Les PLD hiérarchique.

On reprend leur technologies de fabrication en donnant des exemples de produit de la firme Xilinx.

On donne enfin les procédés de leurs programmation

-

-

-

Dans ce chapitre nous allons étudier les points suivant :

- Structure d’un programme VHDL

- Structure d’une description VHDL simple

- Entité

- Les différentes descriptions d’une architecture (de type flot de données, comportemental ou procédural, structurel et architecture de test)

- Process

- Les structures de contrôle en VHDL

- Instructions séquentielles et concurrentes

- Les paquetages et les bibliothèques

-

-

Assignment

DEVOIR à remettre au plus tard le jour de l’examen

Il sera noté 6/6 de la note de TD. Il doit être rédigé avec des feuilles au format A4.

La présentation compte pour la note

Pour tout retard au-delà du 13/02/2022 le matin la note sera 0/6

-

-

-

POUR PREPARER L'EMD ET LE DEVOIR A LA MAISON, J'ai mis a la disposition des etudiants des exercices corriges des tds et autres supplementaires.

-

File

-

File

-

File

-

File

-

-

-

- Réviser les formules de DE Morgan

- Réviser les affectations sélectives vues en cours avec with........ select

-